封装分水岭已至!3D堆叠重新定义Edge AI 竞争格局

边缘人工智能正迎来结构性转折点。随着多模态推理加速渗透汽车电子、工业机器人、消费电子与安防四大场景,其设备数量以17%的年复合增速迈向2030年20亿台规模。与云端动辄10,000TOPS的算力配置不同,端侧仅需1–50TOPS算力,却要在0.01–1W功耗、10–1000美元成本内实现实时推理,必须同时兼顾性能、能效、尺寸与热管理。传统平面SoC已难突破三重约束,3D垂直堆叠成为产业共识的破局路径。

从平面转垂直:

封装路线的必然转向

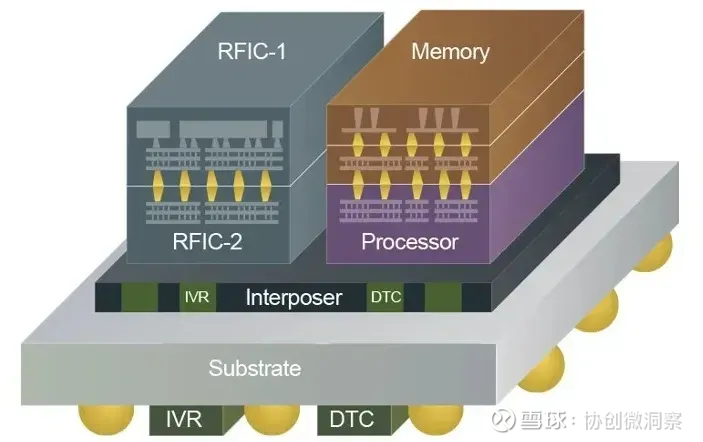

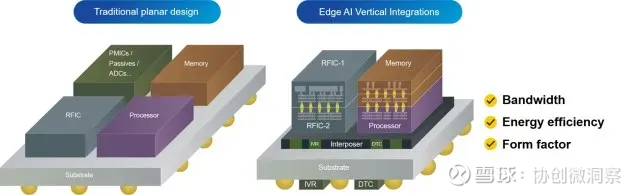

传统平面SoC的扩展瓶颈日益凸显。多模态算法叠加视觉识别、语音交互、运动控制等任务后,片上互连距离拉长,导致数据延迟上升、功耗恶化,系统性能瓶颈已从“晶体管数量”转移到“数据移动成本”。2024–2025年,产业加速切换至3D垂直堆叠路线,通过缩短互连路径、降低RC延迟、提升能效密度,精准匹配端侧多元约束。

这一转向已落地为产业化动作:联电披露的TSV-last、硅中介层、晶圆级混合键合等核心技术平台,均已进入量产或平台化开发阶段。晶圆厂、OSAT(外包半导体封装测试厂商)与系统公司的协同布局,标志着3D封装从概念验证迈入产业化推进期,成为Edge AI的新“基础设施”。

3D垂直堆叠:

为何能成为最优解?

1.破解平面架构物理极限

Edge AI的核心痛点是计算与存储单元的物理距离限制能效。平面扩展模式下,互连距离增加导致数据搬运能耗上升,布线变长引发延迟与信号完整性恶化,功能模块集中造成热密度攀升。随着大模型参数持续增大,平面SoC的规模扩展逐渐陷入“得不偿失”的困境,而3D堆叠将传输路径从毫米级缩短至微米级,从根源上解决问题。

2.系统级优势实现全维度优化

3D垂直堆叠绝非简单“堆芯片”,核心价值源于制造体系重构:其一,互连垂直化通过TSV或混合键合技术,使带宽实现数量级提升;其二,模块按需组合允许处理器、存储等组件采用不同制程节点,兼顾性能与成本良率;其三,中介层可整合电源分配网络、高速通道与去耦单元,联电的硅中介层方案就通过高纵横比电容嵌入,为高带宽链路提供稳定瞬态供电,支撑实时推理的快速电流波动。这意味着先进封装已从连接方式升级为系统级前置设计逻辑。

3.TSV与混合键合构成技术双支柱

TSV-last技术允许成熟节点晶圆完成通孔形成后,再与先进逻辑晶圆堆叠,凭借兼容性强、成本可控的优势,成为当前异构集成的主流路径。混合键合则移除传统微凸点,实现金属–金属与介电–介电直接键合,使互连间距进入微米级,显著降低延迟与功耗,特别适配智能驾驶、工业机器人等实时推理场景。

4.选择性堆叠成为产业共识

垂直堆叠并非适用于所有模块,差异化采用已成行业共识:NPU与Memory组合最能受益,是当前技术落地主战场;ISP、PMIC因对热与噪声敏感,仍适合平面布局;RF、Flash、MEMS等则通过“成熟节点+先进封装”实现成本与性能平衡。未来Edge AI SoC将是多技术节点、多封装形式、多物理域组成的系统级“混合架构”。

Edge AI封装体系:

三大重构方向

1.成本结构决定路线长期分化

端侧产品的价格敏感性,决定了无法沿用云端芯片的高端封装路线。联电“特殊工艺+先进封装”的思路,本质是让RFSOI、MEMS等成熟工艺组件通过3D堆叠获取性能增益,无需迁移至昂贵先进制程。未来Edge AI的成本效率,将极大取决于“工艺节点×封装架构”的优化组合能力。

2.封装能力成为核心竞争焦点

过去三年,晶圆厂加速布局封装业务,核心逻辑是计算体系从“晶圆驱动”转向“系统驱动”,封装成为数据路径效率的关键。围绕TSV-last、混合键合等技术的竞争,将直接影响大模型端侧轻量化、汽车算力布局、工业机器人能效升级的节奏,封装已从生产后段升级为架构前置设计变量。

3.生态协同门槛显著提高

高密度堆叠使测试、验证与质量溯源复杂度倍增:检测设备需识别多层结构缺陷,OSAT需掌握晶圆级堆叠良率管理技术,系统厂商要推动接口与模块标准化。未来12–24个月,生态协同能力将取代单点技术突破,成为先进封装产业化的核心约束。

谁将定义下一代封装形态?

Edge AI的技术演进,已将3D堆叠从“可选先进技术”推向“必需基础配置”。当计算路径、供电网络、热设计与异构模块的耦合不断加深,封装正成为左右系统架构的决定性力量。

核心问题浮出水面:在功耗、成本与密度的多重约束下,下一代Edge AI封装形态将由掌握制造核心的晶圆厂、深耕封装技术的OSAT,还是主导应用场景的整机厂定义?这一答案将直接决定未来五年的产业竞争格局。