多晶硅垂直TFT电稳定性突破!高k栅介质层技术提升AMOLED显示性能

在显示技术向高分辨率、高刷新率、柔性化发展的当下,AMOLED凭借自发光、高对比度、快速响应等优势,已成为高端显示领域的主流技术。多晶硅TFT因具备高有效迁移率、与CMOS工艺兼容等特性,一直是AMOLED背板的核心驱动器件,其性能直接决定了显示面板的驱动电流、响应速度和运行稳定性。

随着显示像素密度的不断提升,传统横向多晶硅TFT面临着难以逾越的瓶颈。一方面,横向TFT的沟道长度依赖光刻技术精度,进一步缩小尺寸易引发短沟道效应,导致器件性能退化;另一方面,AMOLED像素单元对驱动电流的需求持续增加,横向结构的电流密度已难以满足高亮度、高刷新率的显示需求。在此背景下,多晶硅垂直TFT应运而生,其沟道长度由薄膜沉积厚度决定,而非光刻精度,不仅能轻松实现短沟道设计,还能通过增加侧壁通道宽度提升驱动电流,同时潜在的高截止频率使其具备高速运行能力,成为适配下一代AMOLED 显示的理想选择。

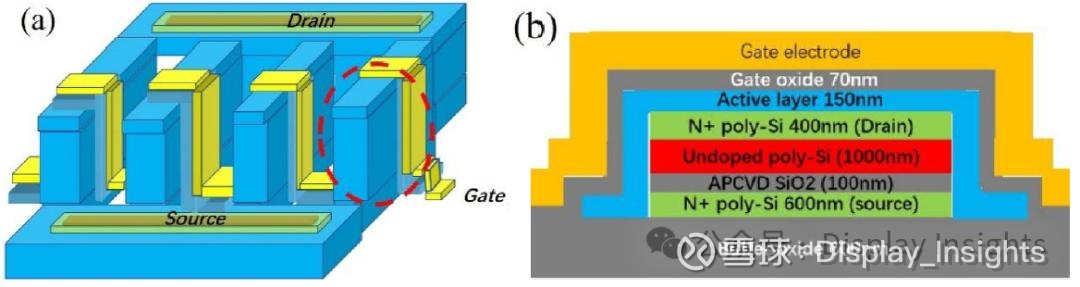

图1. (a)具有8个侧壁的四齿梳状多晶硅垂直TFT示意图;(b)单个齿的横截面图

然而,垂直TFT的商业化应用仍面临核心障碍 —— 电应力不稳定性。在AMOLED显示的长期工作过程中,TFT需承受持续的电应力作用,容易出现阈值电压漂移、迁移率下降等问题,最终导致OLED发光亮度不均、寿命缩短。此前的研究多将不稳定性归因于沟道与栅介质层界面的深能级态影响,但研究人员发现,这一机制无法完全解释垂直TFT的电性能衰减规律。此外,垂直TFT的制备工艺复杂度、器件可重复性等问题,也制约着其规模化应用。

近期,南京邮电大学集成电路科学与工程学院联合法国雷恩大学电子与数字技术研究所OASIS实验室,在多晶硅垂直TFT研究中取得重要研究成果。研究人员通过5 Mask工艺成功制备出四齿梳状多晶硅垂直TFT,系统阐明了其电应力不稳定性的核心机制,并验证了高k栅介质层对稳定性的显著提升作用。相关研究成果发表于《Solid-State Electronics》期刊,为AMOLED显示背板的高性能化、高稳定化提供了重要的技术支撑与理论依据。

5 Mask工艺制备垂直结构,多维度解析不稳定性机制

作为长期致力于TFT器件研发的团队,研究人员基于对多晶硅材料特性和垂直器件结构的深刻理解,构建了一套从器件制备、机制解析到性能优化的完整技术方案,核心围绕垂直TFT 的结构设计、工艺实现、不稳定性机制分析及高k介质层改进展开。

1.垂直TFT结构设计与五掩模制备工艺

研究人员创新性地设计了一种四齿梳状多晶硅垂直TFT结构,其核心特点是将活性层沉积于梳状台面的侧壁,通过增加侧壁数量拓展总通道宽度,从而提升驱动电流。器件的沟道长度由源漏之间的未掺杂多晶硅层与SiO₂阻挡层总厚度决定,既保证了足够的长度以缓解短沟道效应,又通过蚀刻选择性优化实现了精准控制。

研究人员在制备该器件时采用5 Mask工艺,具体流程经过反复优化:

a. 首先以硅片为衬底,通过标准RCA清洗后,采用常压化学气相沉积技术制备厚SiO₂缓冲层,避免衬底污染;

b. 随后依次沉积N型重掺杂多晶硅、SiO₂层、未掺杂多晶硅层和N型重掺杂多晶硅四层结构;

c. 通过两次光刻和反应离子蚀刻形成梳状结构并隔离器件,其中第二次部分蚀刻借助激光干涉仪精准抵达底部重掺杂层,形成源漏区域;

d. 之后沉积未掺杂多晶硅作为侧壁活性层,经再次RIE蚀刻定型;

e. 栅介质层采用SiO₂,通过APCVD沉积后致密化,最大限度消除缺陷;最后通过真空蒸发沉积铝层,经湿法蚀刻形成源、漏、栅接触电极。

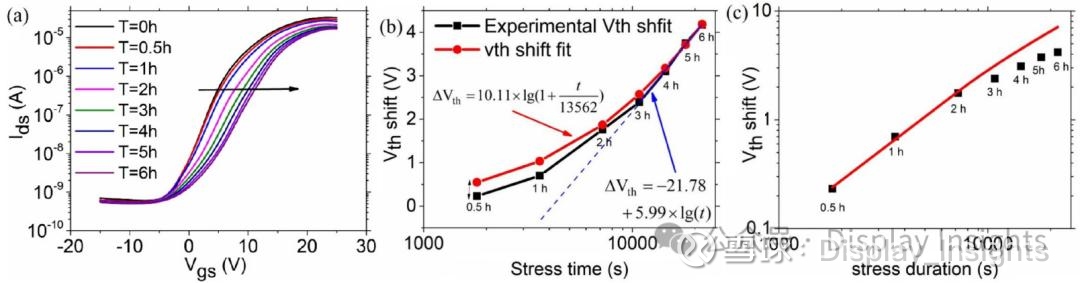

图2. (a)不同栅极偏压应力时长下垂直TFT的转移特性;(b)半对数坐标中的阈值电压漂移;(c)对数-对数坐标中的阈值电压漂移

相较于传统横向TFT的4 Mask工艺,垂直TFT新增的一道掩模用于实现活性层图案化与器件隔离,虽略微增加了工艺复杂度,但通过侧壁活性层设计获得了更大的通道宽度,为AMOLED驱动提供了充足的电流储备。

2.电应力不稳定性机制解析方法

为精准揭示垂直TFT的电应力不稳定性本质,研究人员设计了一种系统的测试与分析方案:对器件施加15V栅极应力电压,持续时间从0.5小时到6小时,在漏源电压0.1V条件下测试不同应力时长后的转移特性,提取阈值电压、有效迁移率、亚阈值摆幅等关键电参数;研究人员计算器件的态密度,通过泊松方程推导界面态密度,结合阈值电压漂移的半对数与对数坐标拟合,区分深能级态与栅介质层电荷俘获的影响。

3.高k栅介质层优化方案

针对栅介质层电荷俘获导致的不稳定性,研究人员提出采用高k栅介质层替代传统SiO₂的优化方案。选择Al₂O₃作为高k材料,其介电常数显著高于SiO₂,在保证同等栅电容的前提下可降低栅极工作电压,进而减小栅介质层中的电场强度,抑制电荷注入与俘获。通过专用工具构建器件模型,模拟高k栅介质层对电性能与电场分布的影响,并在AMOLED 2T1C像素单元中验证其稳定性提升效果。

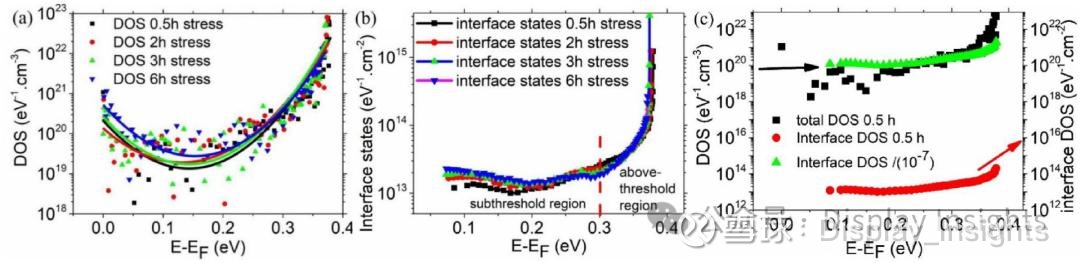

图3. (a)不同应力时长下基于Suzuki法的态密度计算结果;(b)不同应力时长下的界面态密度计算结果;(c) 0.5小时应力时长下态密度与界面态密度的对比分析

样品性能研究:揭示电荷俘获核心机制,高k介质层使OLED电流误差率降至3.8%**

经过系统的实验测试与模拟分析,研究人员的技术方案取得了显著成效,不仅阐明了多晶硅垂直TFT电应力不稳定性的核心机制,更通过高k栅介质层优化实现了稳定性的大幅提升,为其在AMOLED中的应用奠定了坚实基础。

1.垂直TFT基础电性能与不稳定性机制

制备的四齿梳状多晶硅垂直 TFT 展现出良好的基础电性能,初始阈值电压为8.87V,有效迁移率达2.51cm²/V.s,亚阈值摆幅2.734V/dec,能够满足AMOLED驱动的基本需求。通过不同时长的电应力测试,研究人员发现器件的不稳定性呈现明显的两阶段特征:前2小时内,除阈值电压漂移外,有效迁移率和亚阈值摆幅均出现轻微退化,这归因于沟道或界面深能级态的影响;3小时后,仅观察到阈值电压持续漂移,迁移率和亚阈值摆幅保持稳定,表明栅介质层电荷俘获成为主导机制。

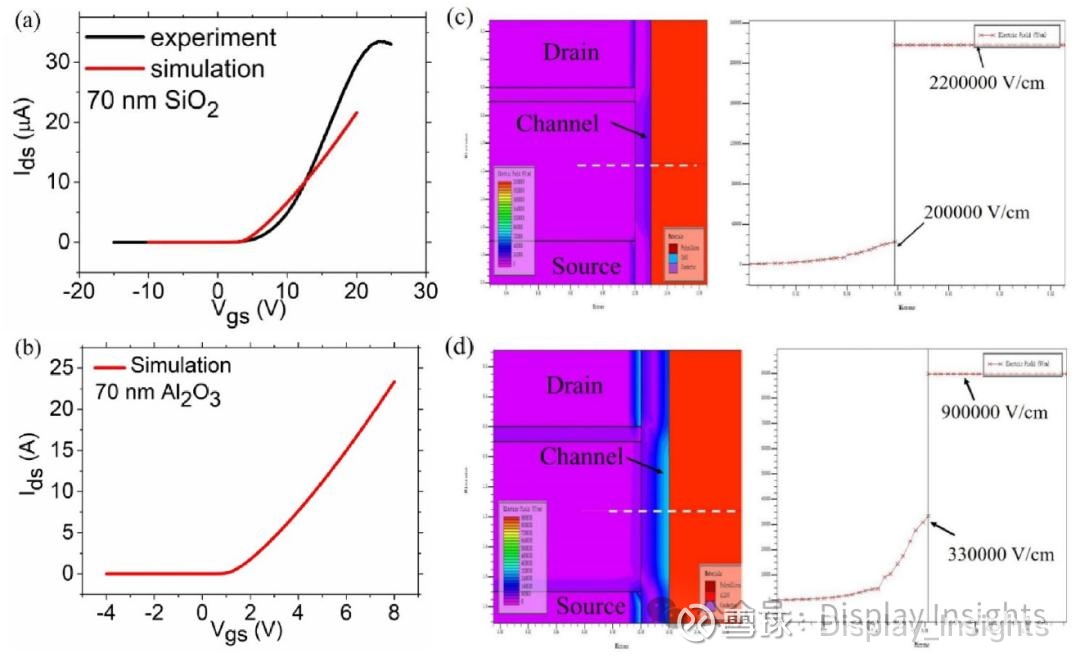

图4. (a)采用70纳米SiO₂栅介质层的垂直TFT模拟转移特性;(b)采用70纳米Al₂O₃栅介质层的垂直TFT模拟转移特性;(c)采用70纳米SiO₂栅介质层且栅极偏压为15V时,垂直TFT的模拟电场分布;(d)采用70纳米Al₂O₃栅介质层且栅极偏压为6V时,垂直TFT的模拟电场分布

态密度与界面态密度计算结果进一步验证了这一结论:不同应力时长下,界面态密度基本保持一致,仅0.5小时应力时存在轻微偏差,说明界面深能级态仅在应力初期产生微弱影响;而总态密度的变化规律与阈值电压漂移趋势吻合,证实栅介质层电荷俘获是导致器件长期电不稳定性的核心原因。通过半对数坐标拟合,阈值电压漂移符合电荷俘获机制的对数时间依赖关系,拟合公式为 ΔVth=10.11×log (1+t/13562),与实验数据高度吻合。

2.高k栅介质层优化效果显著

采用70nm Al₂O₃高k栅介质层替代传统SiO₂后,器件的电稳定性得到根本性提升。专业工具模拟结果显示,在获得相同导通电流的情况下,Al₂O₃栅介质层的栅极工作电压可从15V降至6V,栅介质层中的电场强度从2.2×106V/cm降至9×105V/cm,大幅抑制了电荷注入与俘获。

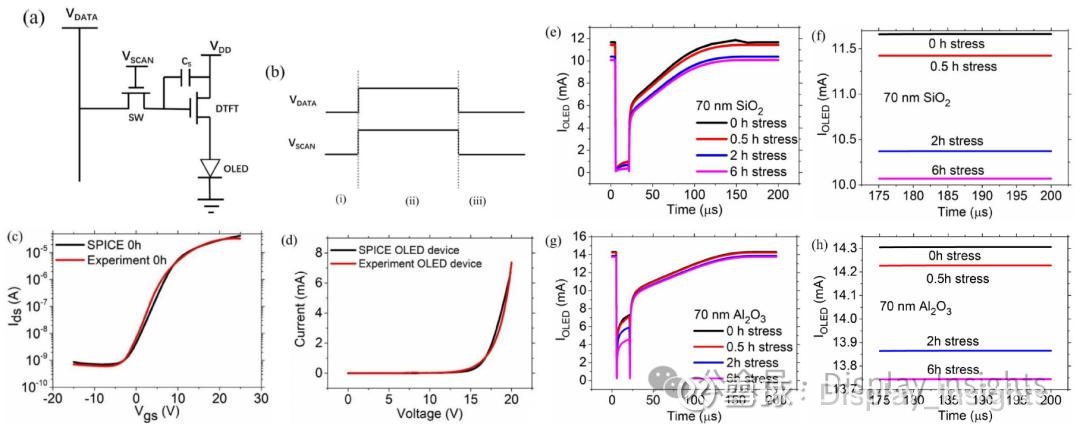

图5. (a) AMOLED像素单元的2T1C结构;(b) 2T1C结构的时序图;(c) 垂直TFT的SPICE仿真与实验特性曲线;(d) OLED器件的SPICE仿真与实验特性曲线;(e)、(f)采用70纳米SiO₂栅介质层的TFT驱动OLED的瞬态电流仿真结果;(g)、(h)采用70纳米Al₂O₃栅介质层的TFT驱动OLED的瞬态电流仿真结果

在AMOLED 2T1C像素单元测试中,这一优化效果更为直观:采用SiO₂栅介质层的TFT在6小时电应力后,OLED驱动电流从11.7mA降至10.1mA,误差率达13.6%;而采用Al₂O₃高k栅介质层的TFT,相同应力条件下电流仅从14.3mA降至13.75mA,误差率仅3.8%,稳定性提升近3倍。尽管3.8%的误差率与高端AMOLED要求的0.5%仍有差距,但已达到实际应用的允许范围,后续通过进一步优化高k材料介电常数、改善栅介质/沟道界面质量或引入补偿电路,有望实现更优的稳定性。

此外,研究人员制备的垂直TFT通过SPC技术获得了均匀的晶粒尺寸,器件可重复性良好,四齿梳状结构的侧壁设计有效提升了总通道宽度,驱动电流满足AMOLED像素单元的发光需求。5 Mask工艺虽比横向TFT多一道掩模,但通过工艺优化已实现稳定量产,为后续规模化应用提供了可能。

DOI:10.1016/j.sse.2025.109263