AMAT:混合键合真正的门槛,在 CMP

$华海清科(SH688120)$

原文来自:芯联汇

键合不是第一道关,CMP 才是决定良率与尺度的起点

最近小编重新读了一遍 AMAT(应用材料)发布的《CMP for Hybrid Bonding》 这份材料。

如果只是把它当成一篇 CMP 工艺说明,其实是看轻了;真正读完之后,我的感受反而很清晰:

在混合键合时代,CMP 已经不再只是“抛平表面”,而是在决定 3D 集成这条路,究竟能不能走下去。

很多键合问题,看起来发生在 bonding 这一步,但根源,往往早就写在 CMP 交出的那张“表面答卷”里。

一、这份文档到底想说明什么?

这不是一篇“讲 CMP 原理”的基础材料,而是在反复强调一个事实:

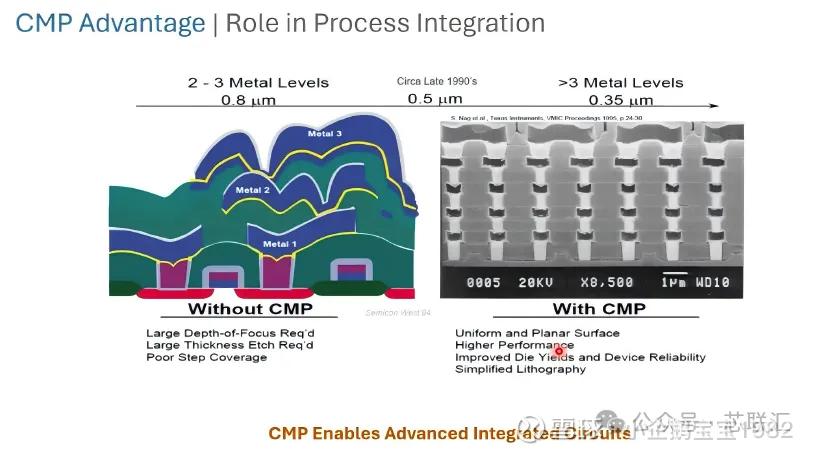

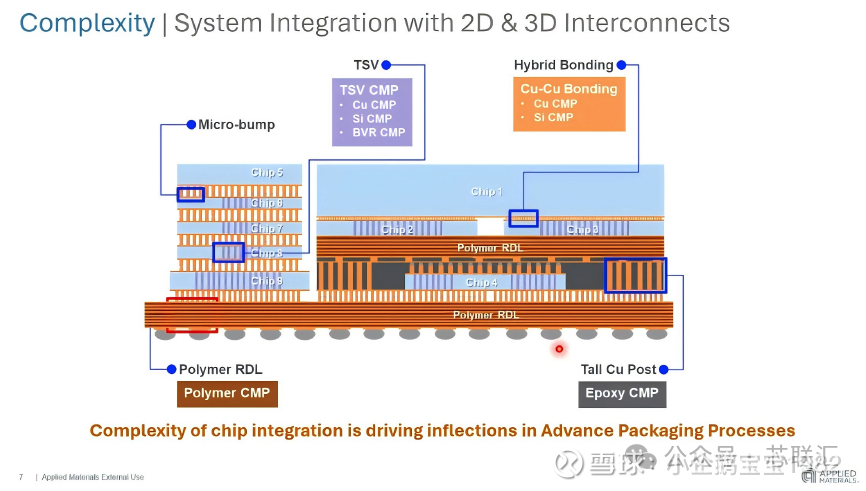

随着 2.5D → 3D → W2W 混合键合推进,CMP 已经从“辅助工艺”,升级为“系统级成败因子”。

二、核心逻辑主线(非常清晰)

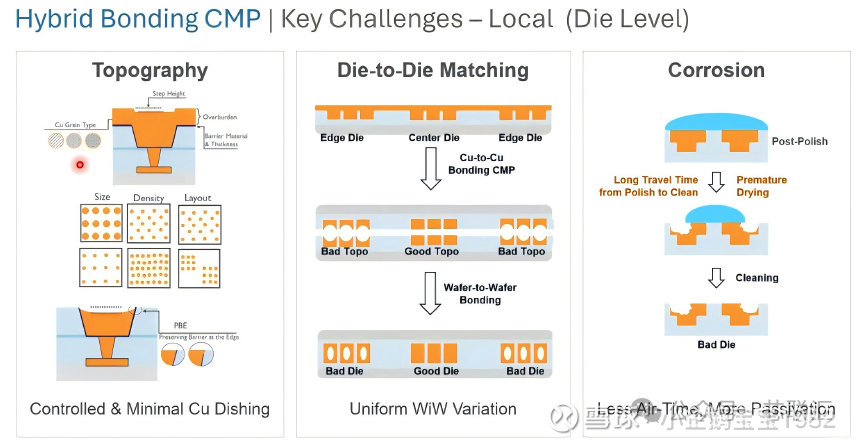

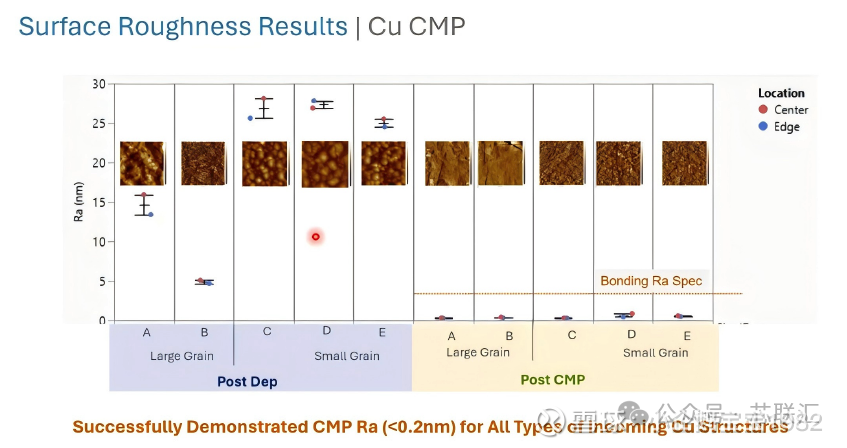

① 混合键合的难点,本质都在“表面状态”

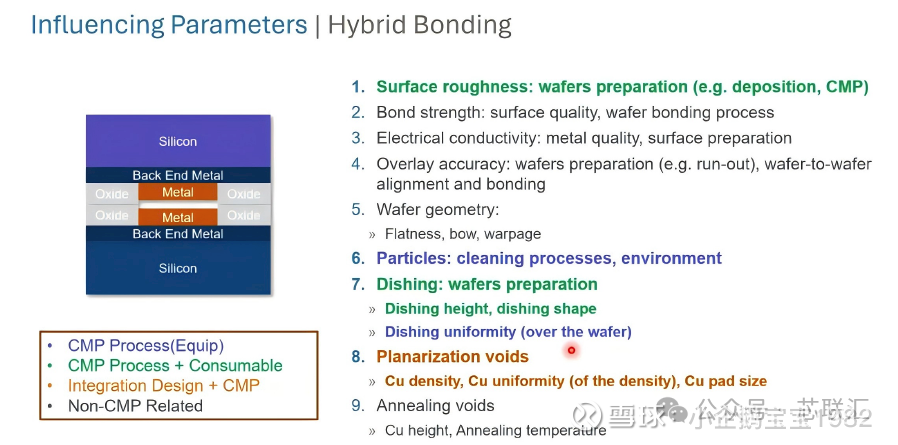

从文档中对 Hybrid Bonding 影响参数的系统拆解可以看到:

CMP 直接决定的关键指标包括:

表面粗糙度(RMS)

Cu dishing 高度与形貌

Cu 密度与均匀性

W2W / Die-to-Die overlay 匹配

Planarization void / bonding void

👉 换句话说:键合失败,90% 不是“键合设备”的问题,而是 CMP 给了一个不合格的表面。

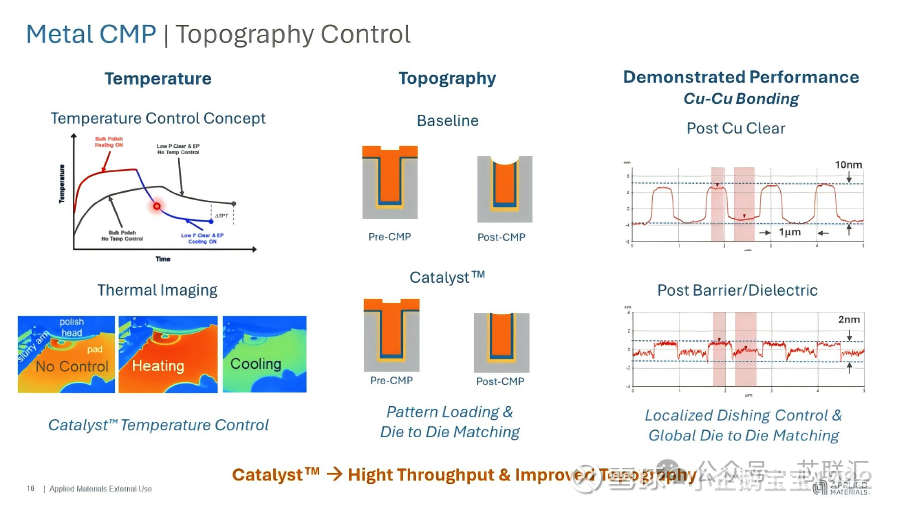

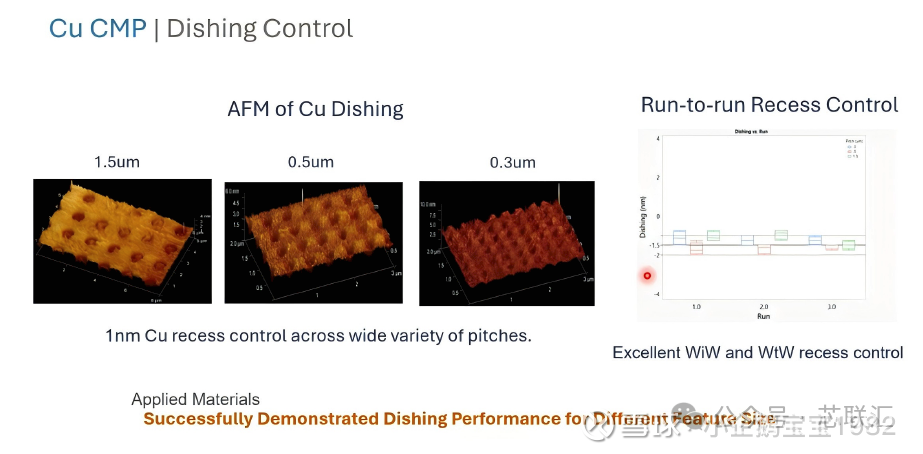

② Cu-Cu Hybrid Bonding,对 CMP 的要求“陡然升级”

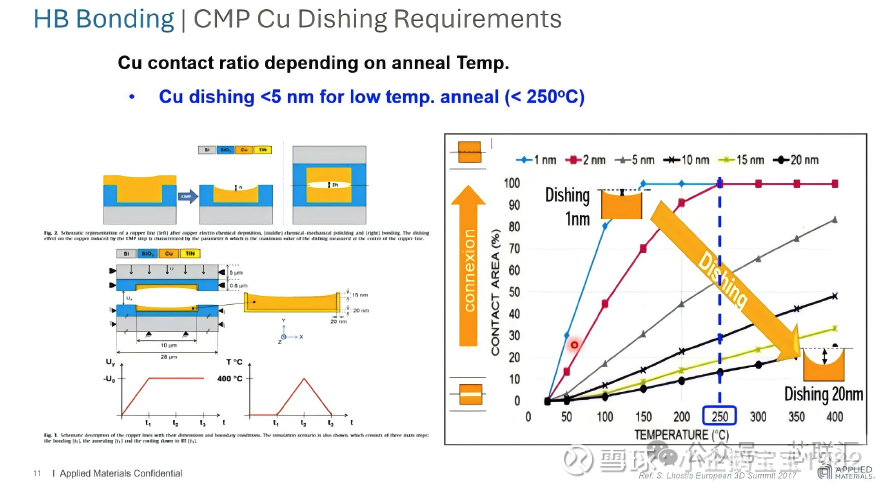

文档反复强调:

低温退火(<250 °C)条件下

Cu dishing 必须 < 5 nm

否则 Cu 接触率快速下降,bond strength 和电性能同时劣化

同时,CMP 需要在以下维度同时成立:

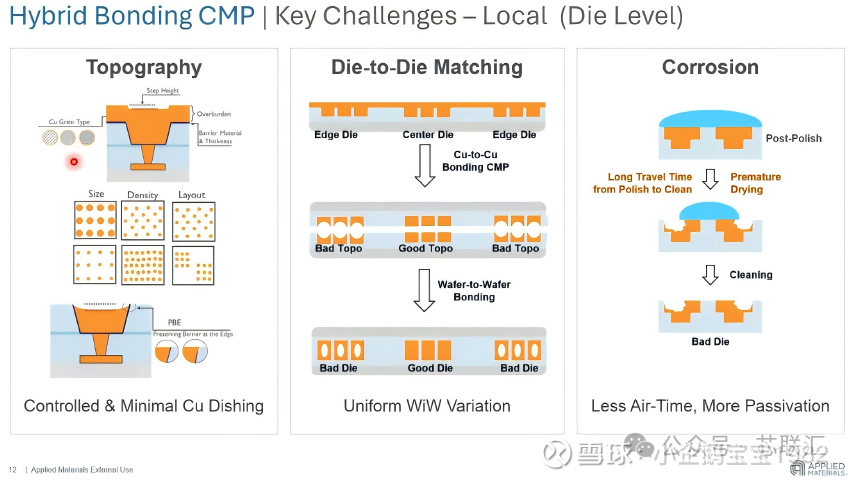

局部(within die)dishing 可控

全片(WIW / WTW)非均匀性极小

die-to-die topography 高度匹配

👉 这已经远超传统 BEOL Cu CMP 的控制难度

③ Hybrid Bonding 把 CMP 推进“闭环控制时代”

文档明确给出的趋势是:

Multi-zone polishing head

In-situ sensor(实时厚度/压力/温度)

RTPC-XETM 实时过程控制

Run-to-run recess / dishing control

结论非常直白:

没有实时计量与闭环控制的 CMP,无法支撑 <2 µm、甚至 <1 µm pitch 的混合键合。

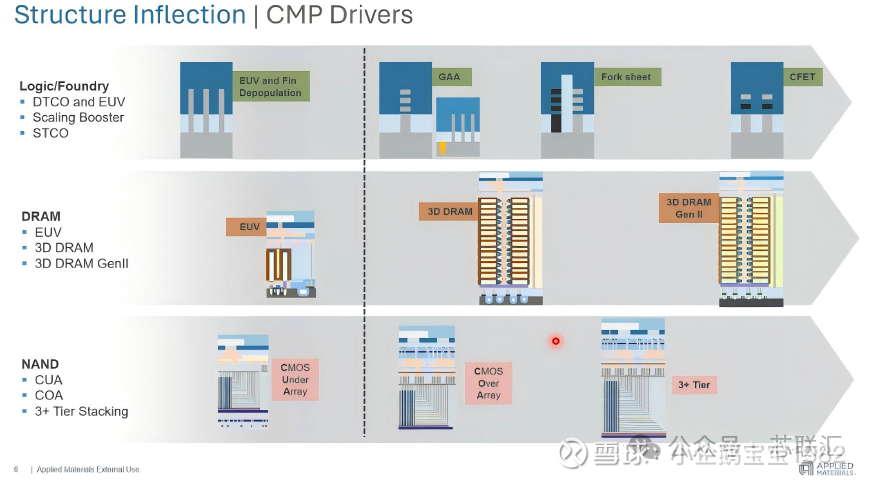

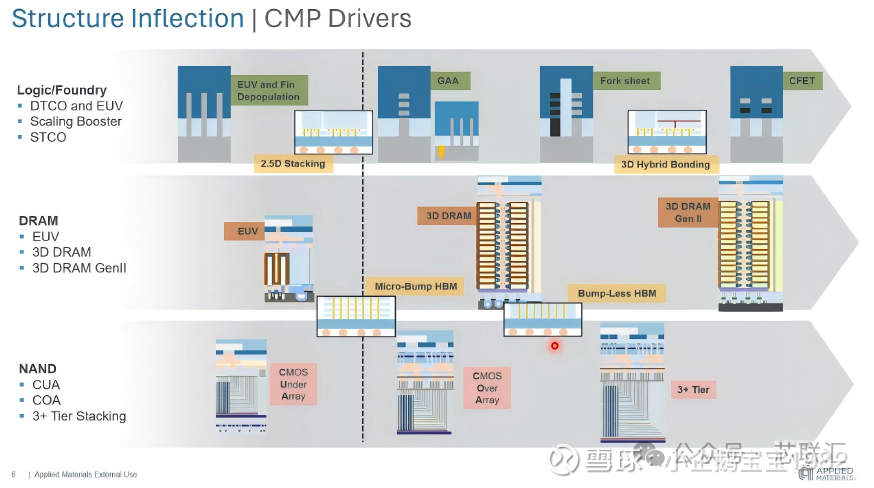

④ CMP 正在被“先进封装结构”反向定义

在结构演进页,文档把 CMP 与以下趋势直接绑定:

Logic:GAA / CFET + 2.5D / Hybrid Bonding

DRAM:HBM → Bumpless HBM → W2W

NAND:CMOS under array / 3D stacking

3D DRAM / CoA 架构 → W2W pitch < 0.5 µm

这意味着:

未来 CMP 的工艺窗口,不再由单一器件决定,而是由“系统级 3D 集成复杂度”决定。

三、这份文档的“隐含判断”(非常重要)

虽然全文在讲 CMP,但核心态度其实是:

Hybrid Bonding ≠ 单一工序突破

而是 CMP × 清洗 × 表面活化 × 退火 × 对准 的系统协同

其中 CMP 是第一个、也是最不可妥协的基础

四、小编总结

混合键合真正的难点,从来不在“能不能键合”,而在“能不能把表面交出来”。

当 pitch 进入亚 2 µm、工艺窗口被压缩到纳米级,CMP 已经不再是一个可以靠经验“兜底”的工序,而是决定良率、可靠性、乃至整条 3D 集成路线能否继续推进的第一道门槛。

从这个角度看,《CMP for Hybrid Bonding》讨论的并不是CMP 要不要升级,而是在明确告诉行业:

未来混合键合能走多远,取决于 CMP 能不能先走到位。