hkyo

· 福建

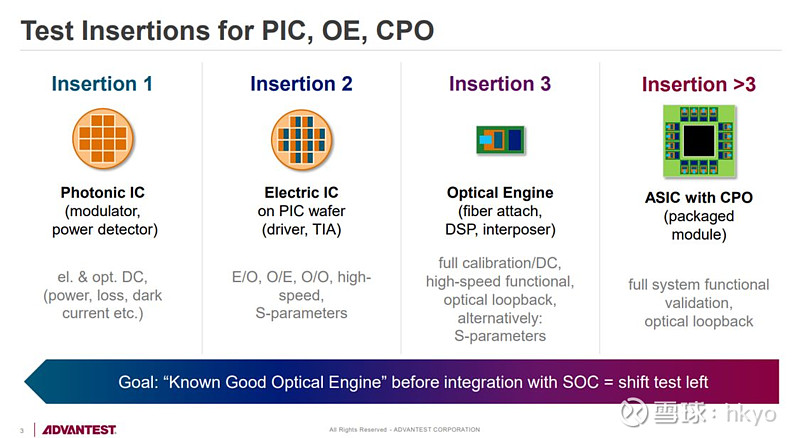

CPO (共封装光学) 测试至关重要,因为失效成本极高。 一旦光学引擎与交换机芯片封装在一起,任何缺陷都可能危及整个组件,而不再仅仅是损失一个可更换的模块。CPO 的测试流程分为四个连续阶段,每个阶段都面临着独特的技术挑战、设备需求和供应商生态。

第一阶段:晶圆级单晶圆测试 (Wafer-Level Single-Die Test)

在键合之前,EIC(电集成电路) 和 PIC(光集成电路) 会在晶圆级分别进行测试。

EIC: 采用标准的 CMOS 晶圆抽检(无需新设备)。

PIC: 需要新型的双面电光探测技术——这也是目前所有新设备投入的重点所在。

第二阶段:双面晶圆级测试 (EIC + PIC)

在 EIC 和 PIC 通过混合键合(Hybrid Bonding)、引线键合(Wire Bonding)或倒装芯片(Flip-chip)技术键合在一起后,成组的晶圆在切割前将作为集成电光(E/O)单元进行整体测试。

第三阶段:晶粒级 EPC 测试 (Die-Level EPC Test)

切割后的单个光学引擎晶粒会进行独立测试。这是进入永久封装前的最后一道关卡。

第四阶段:最终测试 / 系统级测试 (SLT)

完成封装的 CPO 交换机(包含 ASIC + 光学引擎 + 封装)将进行全功率系统级测试。数千瓦量级的热管理是这一阶段最具决定性的挑战。