$罗博特科(SZ300757)$ 不涨归不涨,学习不能停!

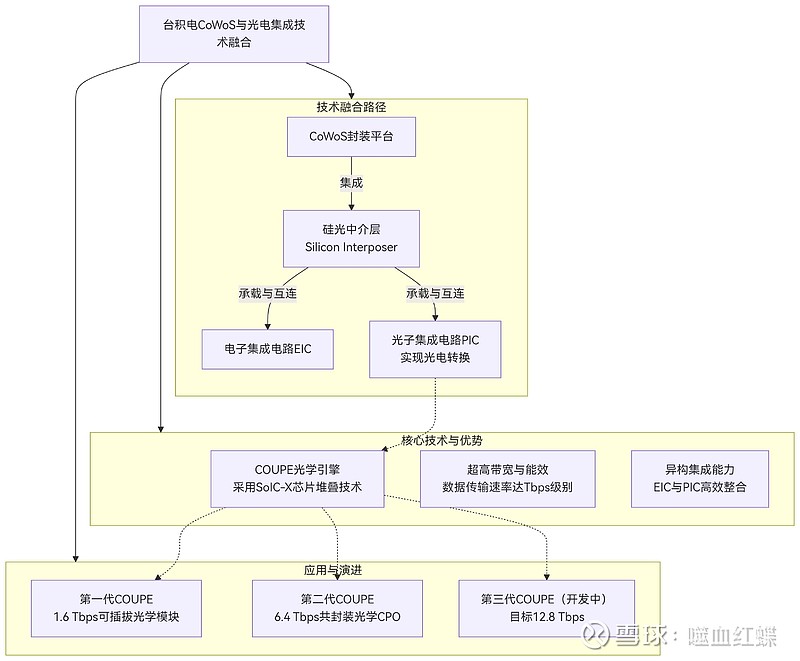

台积电正在将CoWoS封装技术应用于光电集成领域,主要是通过与其硅光子(Silicon Photonics, SiPh)技术和COUPE(紧凑型通用光子引擎)等先进技术平台结合来实现,旨在满足未来高性能计算对高速、低功耗数据传输的迫切需求。

CoWoS 技术为光电集成提供了关键的基础承载平台,它通过其先进的封装能力,能够集成包含光导路径的硅光中介层(Silicon Interposer),从而支持光子集成电路(PIC) 和电子集成电路(EIC) 的高密度互连。

核心技术:COUPE光学引擎

台积电的 COUPE(Compact Universal Photonic Engine,紧凑型通用光子引擎) 技术是实现光电共封装的核心。它采用了台积电的 SoIC-X 芯片堆叠技术,将负责计算和控制的电子集成电路(EIC) 堆叠在负责光电转换的光子集成电路(PIC) 之上,形成一个紧密整合的三维立体结构。这种结构能实现最低的阻抗和更优的能效。

将CoWoS用于光电集成带来了显著优势:

超高带宽与能效:硅光子光互联的数据传输速率远高于传统电互联,能满足AI/HPC对带宽的巨量需求(台积电路线图目标高达12.8 Tbps),同时功耗显著降低。

异构集成与小型化:CoWoS允许将不同工艺、功能的芯片(如EIC、PIC、可能的内存等)集成在一起,减小了封装体积,提高了集成密度。

降低延迟:光连接更接近处理器本身,缩短了数据传输路径,减少了延迟。

应用与未来演进

台积电计划在2026年推出基于CoWoS封装技术整合的共封装光学(CPO)模块。其技术演进路线清晰:

第一代COUPE:集成到1.6 Tbps的可插拔设备中。

第二代COUPE:作为共封装光学器件集成到CoWoS中,支持6.4 Tbps。

第三代COUPE:目标是实现12.8 Tbps的板上光学连接。

为了支持包括光电集成在内的先进封装需求,台积电正在大幅扩充CoWoS产能,预计到2026年底,月产能将增至9万片晶圆。

需要注意的点:

CoWoS是“平台”而非“功能”:CoWoS本身不直接提供光电转换功能,而是作为一个高性能的封装平台,能够集成具备光电转换能力的硅光子芯片(如PIC)和传统电子芯片。

技术尚未大规模量产:基于CoWoS的光电共封装技术(CPO)仍处于发展和推进阶段,尤其缺乏光电一体的清洁、测试和修复设备来提升良率和产能,预计2026年才能推出相关产品。

总结:

台积电将CoWoS这一强大的封装平台与创新的硅光子技术、COUPE光学引擎技术相结合,为下一代数据中心和AI/HPC系统打造高性能、高带宽、低功耗的光电互联解决方案。这代表了半导体行业发展的前沿方向,即通过先进封装和异构集成来“超越摩尔定律”。