罗博特科系列四-3-1:第一大部分:从全球先进算力版图的阵眼——台积电CoWoS封装平台说开去

罗博特科系列四-3-1:英伟达与博通、AMD反叛军们的制霸权之争,从先进封测到集群互联,生态博弈白热化到底谁最渔翁得利(第一大部分:从全球先进算力版图的阵眼——台积电CoWoS封装平台说开去)

四-1和四-2早就写好了,四-3拖了很久,其实不单是因为作者懒,而是最近一个多月,海外AI算力图景演化与生态博弈的进展实在太快,隔几天就来Break News,因此,我需要耐心等待这些信息的主要碎片拼凑完整,才能试着在此基础上,构建出一个相对更清晰的关于未来路线和趋势的素描草图。这也仅仅是寥寥的、远不精确甚至将来可能看来有大谬误的“山水画”而已。所以,看官们也就当个意境山水图去粗看,切莫当真。

接着说。近期,包括英伟达、OpenAI、博通和AMD等巨头依次宣布了一系列技术进展和合纵连横的消息后,并且与作者之前推演的产业趋势越来越吻合的时候,我突然心定福至,觉得写的时机基本成熟了,可以完成4-3的内容了。那么接下来,请搬来你的小板凳,带着看戏的心态,秉着放松的心情,听我把近期所思所想,予尔娓娓道来。信息量和思考量都很大,算是呕心沥血完成,但我还是尽量做到简化和简洁,尽管如此,篇幅估计还是不会太小。能仔细看完的,都是很有耐心的人。

写的过程中,一再压缩,一再超字,恐怕四-3要再拆分一下了,第一大部分是台积电CoWoS封装平台的详细分析。第二大部分是英伟达与博通、AMD反叛军之间的行业生态圈和话语权的制霸之争,当然也会写到海外大厂的平衡策略。渔翁得利这个事,分拆在第一大部分和第二大部分里分别说,今天先把拖延持久的第一大部分写完。

一、前言:半导体行业的内容极其繁琐,哪怕单拎出来一个算力板块,分析也不知道从何下手,我也一直纠结于此,感觉沉浮在知识爆炸和信息乱流的汪洋大海,乱花迷眼,头昏脑涨。后来,资料越看越多了,终于也找到了一个可以提纲挈领的办法,那就是盯紧最先进的也是最紧缺的台积电的CoWoS封装平台,尤其是它的技术演化趋势、产能扩张指引以及下游客户比例,理解这些,相当于笼统理解了最前沿的算力技术图和实力热力图,原来混混沌沌的事情,也就慢慢变得清晰起来,思虑也清静了。

二、台积电CoWoS封装平台技术演化史:全球最强算力的诞生地和驱动力

这个精彩故事,应该从台积电2008年成立的一个技术研发部门说起:

2008年,台积电成立了一个叫集成互连与封装技术整合部门(IIPD),看名字就知道,研究的,是用新的封装技术实现新的集成互联。那会,台积电可能就已经意识到摩尔定律的终点越来越近了。这就是所谓的远见(这不正像我们正在投资臭萝卜这件事一样吗?),台积电发展到现在的行业老大地位,绝不是单纯的侥幸,而是远见和战略的胜利。

2010年,台积电启动了2.5D硅中介层研发(注释:硅中介层是核心铺底技术,可以理解为盖超级商业中心的优质地皮、地下打桩以及基础规划),这代表着最核心的基于中介层(材料学)的集成互联和后道封装的技术线路确定了。

2011年,台积电推出首代CoWoS,基于65nm工艺制造的硅中介层,支持0.25μm线宽和四层布线(铜互联)。一个全新的时代,就这样缓缓开启了。

2012年,这一年很重要,详细点说,台积电与赛灵思(Xilinx)合作推出首款采用CoWoS封装的量产产品——Virtex-7HT系列FPGA,基于28nm的工艺制造。题外话,赛灵思是FPGA的鼻祖,后面被AMD以近500亿美金的价格收购了。

这款台积电CoWoS封装出品的首个量产产品,对台积电和CoWoS的发展意义重大:

🔥Chiplet设计范式的首次商用和量产:将大单片FPGA拆分为4个独立的小芯片(Chiplet),通过硅中介层实现集成互连,解决大芯片良率问题(从<10%提升至80%+)。我理解就是化难整为易零,逐个突破并重新组合的思路,很东方的系统设计思维观。所以,到了封装和模型阶段,你会发现华裔越来越厉害,因为文明的尽头,是混沌和模糊,适合系统和矛盾思维,这就是华夏底层思维的优势。

🔥硅中介层的技术验证:硅中介层采用台积电65nm工艺,面积约1000mm²(你可以理解为地皮大小),集成4层铜互连(你可以理解为地下管网和通讯线路),最小线宽0.4μm,支持20万+个微凸块(间距45μm),芯片间通信带宽达10Tb/s,远超传统PCB的Gb/s级。

🔥HBM集成的早期探索:早期版本集成4颗HBM1内存,验证了逻辑芯片与高带宽内存的异构集成可行性。异构集成也将成为未来半导体功能进化的重要方向。

Virtex-7HT产品通过CoWoS实现了“功能分区、性能集中”的设计和量产,为后续NVIDIA GPU的模块化设计奠定工艺和技术基础。尽管初期,台积电只有赛灵思一家客户,但该产品验证了CoWoS的技术价值,也促使台积电持续投入研发,最终形成了今天台积电后道先进封装集大成者的行业老大地位。

2014年,第二代CoWoS问世,硅中介层面积扩大至1150mm²,中介层尺寸突破1.5倍光罩(光罩是一个重要概念,你可以理解为有效光刻尺寸)。这个阶段,还是赛灵思的FPGA产品在使用这个平台量产集成产品。

2016年,又是一个里程碑,第三代CoWoS问世,中介层尺寸没有大的变化,但首次支持4颗高速HBM2(16GB)堆栈集成,带宽达732GB/s,并率先被英伟达的16纳米制程的GP100采用,也是OpenAI开发GPT-1所用的算力卡。从工艺源头来说,AI算力发展的分界线,也许正是从2016年开始的。考虑量产时间线和工艺参数,包括英伟达的GP100(首次引入NVLINK高速互联)、V100(12纳米,首次应用Tensor Core加速矩阵计算)和A100(7纳米)应该都是在三代平台做出来的。

2019年,第四代CoWoS问世,中介层扩大到2倍光罩的曝光面积,大约1700mm²,可以装载1颗SoC+6颗HBM2(48G)。四代平台支撑了H100量产。

2020年,第五代CoWoS问世,中介层面积突破2500mm²(3倍光罩),支持2颗SoC+8颗HBM2E(128GB),带宽提升至3.35TB/s。五代平台支撑了一部分H200量产。

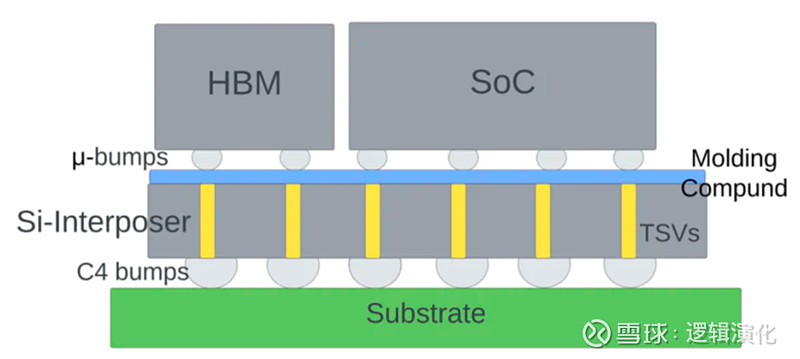

从2011年的第一代,到2020年的第五代,都可以称为CoWoS-S(后面的那个S是硅中介层的意思),基本工艺图如下所示:

大家看到的那个Si-Interposer就是硅中介层。CoWoS(Chip-on-Wafer-on-Substrate)从生产过程上分成两部分,前面的CoW是工艺复杂度最高的封装部分,主要由台积电自己完成,而后面的oS部分相对简单一些,主要由台积电的合作伙伴日月光完成。前阵子,日月光产能跟不上,急得台积电不得不亲自下场,帮着、催着日月光扩后道oS部分的产能。

2020年后,CoWoS进入到多技术线路并进的阶段,除了一直迭代升级到第五代并正在推进第六代的CoWoS-S6外,又出现了CoWoS-R和CoWoS-L两个线路,因此中介层一直是CoWoS技术研发的核心领域。台积电第一阶段的研发任务是给CoWoS-S持续做加法,扩大光罩面积,增加布线密度,实现逻辑-存储更大面积和程度的布局与集成。但是进行到第六代之后,难度越来越大,成本也越来越高。因此,出现了R和L这两个改良版。我理解这个阶段,开始从做加法变成了做性能加法(S6开发)+做重组减法(减硅层占比,加聚合物层,实现材料重组)的技术并用和经济平衡。

2022年,CoWoS-R问世,引入重新布线层(RDL)替代硅中介层,降低成本并支持更大尺寸封装(2500mm²以上)。这个线路简化了中介层,牺牲部分性能,布线密度和带宽仅为S的一半,高频信号损耗也增加,但提高了面积,提升了工艺稳定性和良率,降低了封装成本,适用于要求更低的消费电子、汽车电子和边缘AI等领域。你可以理解为CoWoS-S的平民普及版。

2023年,CoWoS-L问世,采用局部硅互连(LSI)+RDL中介层,在关键区域保留硅的高性能,其余部分用RDL降低成本。这是对CoWoS-S发展到第五代之后存在的热应力问题、复杂拼装、良率损失导致的高封装成本问题的一次聪明的妥协。这个思路,通过LSI与RDL的协同设计实现“性能-成本”再平衡,牺牲的布线和通讯性能可控,同时能扩大光罩面积,提升良率(解决大硅层应力等问题),降低了总体成本。预计到2025年,CoWoS-L产能占比将达到54.6%,成为台积电CoWoS目前阶段的主流技术。英伟达即将主卖的GB300就出产自这个封装平台。

由此,CoWoS逐渐完善,而且在加速多技术线路的进化,S站在顶端,定义前沿标杆,R在底部,支撑规模应用,L在中间,架起平衡的桥梁,满足差异化和迫切性需求。目前,台积电仍然在不断推进CoWoS封装平台的技术工艺演进,包括硅中介层的材料学改进与工艺优化,如不断优化“局部硅互连(LSI)+有机RDL”混合中介层,实施热管理优化(相变材料PCM应用、梯度CTE过渡层等),强化缺陷检测与控制(AI驱动检测、同步辐射X射线检测等),不断提升平台良率,提升产能扩张,降低封装成本。

还有一个更重要的趋势,就是CoWoS正与SoIC、CPO加快三位一体的深度整合,不断实现“光-电-逻辑-存储”全栈高密度、高互联集成。比如台积电开发的紧凑型通用光子引擎(COUPE)基于SoIC堆叠技术,将电集成电路(EIC)与光子集成电路(PIC)垂直堆叠。COUPE再与CoWoS-L耦合使用,形成“先进封装+光电互联”的新技术护城河,计划使CPO模块在2026年实现1.6Tbps以上带宽,支撑超大型AI算力集群的高速光电互联。台积电也计划在2026年将更大比例的CoWoS产能分配给CPO相关产品,主要服务于英伟达Rubin架构服务器和博通交换机等划时代新产品。

三、从产能发展和扩张指引来说:

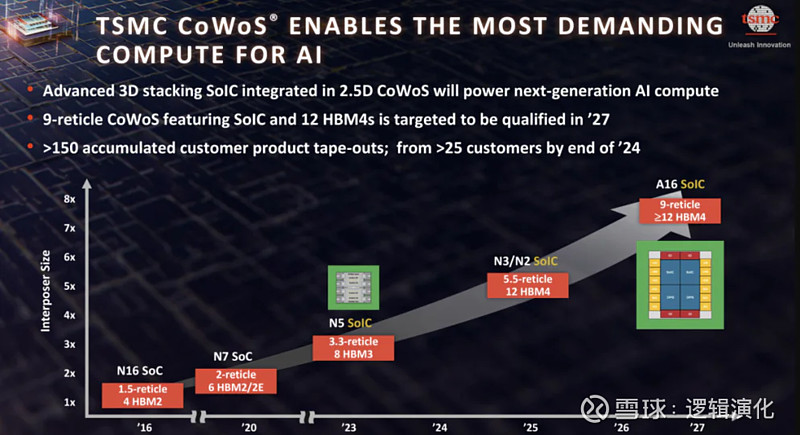

先上图,这张图比较简洁得展示了CoWoS的发展历史和发展趋势:

其中2016年、2020年、2023年、2025年以及计划的2027年,都是比较重要的发展里程碑,可见目前台积电的CoWoS封装基本是两年进行一次大升级,而且研发周期还在加速。这张图也展示了历次主要升级的关键参数变化,包括光罩(reticle,也叫mask)的扩大,采用的SoIC芯片等级(如N16、N7、N5、N3、A16等),HBM集成数量和等级(如HBM4,12颗)。随着CoWoS封装技术能力的不断迭代和下游需求扩大,尤其是2018年后AI算力需求横空出世,其产能呈现爆发式的增长并延续至今:

🔥早期探索:2011年,首代CoWoS量产时,产能不足1000片/月,主要服务于赛灵思FPGA等小众高端市场。2015年,受限于硅中介层尺寸(仅775mm²)和TSV(硅通孔)工艺成熟度,产能扩张缓慢。产能约为2000片/月,客户集中在网络芯片领域。

🔥规模化商用:2016年,CoWoS实现第一次技术大突破,中介层尺寸突破1.5倍光罩,支持4颗HBM2集成,产能提升至5000片/月。从2018年开始,OpenAI大模型训练加速等事件导致英伟达AI算力芯片需求激增,到2019年,A100芯片加速量产,CoWoS产能达到1.5万片/月。这一时期,包括到2020年阶段,英伟达占用了80%左右的CoWoS产能去生产英伟达的先进算力芯片。

🔥算力大爆发驱动:2021年,第五代CoWoS-S支持8颗HBM2E,产能进一步提升至2.5万片/月。2024年,台积电通过改造南科AP8厂和竹南AP6B厂,产能跃升至3.5-4万片/月,其中CoWoS-L占比逐步达到约30%。

台积电2025年正逐步将月产能提升至6.5-7.5万片/月,主要来自AP8厂全面投产和CoWoS-L良率提升(从75%至85%)。按照我能查到的最新进展(不保真,来自网络信息收集),2025年Q1-Q3,CoWoS月产能维持在5-6万片/月,据说主要是受制于硅中介层供应和EUV光刻机交付延迟,包括日月光的OS产能没跟上。进入到Q4,随着问题解决,南科AP8厂全面投产,单厂贡献约3万片/月,叠加竹南AP6B厂改造完成,产能跃升至7-7.5万片/月。其中,CoWoS-L占比从2024年的不足10%提升至2025年Q4的54.6%,良率提升至85%,成为主流技术,支撑英伟达B300等芯片量产。所以你看,GB300系列产品应该是从Q3末至Q4开始发力。

2026年,台积电计划产能提升目标是11万片/月,主要是南科AP7厂新增4万片/月,其中CoWoS-L占比将超70%,CoWoS-R(升级至R2,改为玻璃中介层)占比提升至15%。届时,高端产能服务的主要产品预计是英伟达的Rubin系列。2027年,产能将进一步提升至13万片/月,并实现9.5倍光罩CoWoS量产。

CoWoS封装的HBM带宽从2016年的732GB/s提升至8TB/s(GB300)。硅中介层面积从1000mm²到突破2500mm²,支持的微凸块(Micro Bump)密度从2016年的49个/mm²提升至2024年的160个/mm²,实现芯片间互连密度的大幅增长。微凸块优化与HBM集成的深度相关,下一代平台,随着HBM4与CoWoS-L2的结合,微凸点密度有望突破250个/mm²,单卡带宽将达30TB/s以上。同时,集成和工艺的精细度和难度也是越来越大。

需要说明的是,尽管台积电升级平台并持续扩产,由于断代的封装领先优势,不论是三星还是英特尔都难以跟上其技术节奏,加上高端算力需求的持续疯狂扩张,导致CoWoS平台一直是制约英伟达量产新产品的核心瓶颈环节。在肉眼可见的2027年以内,CoWoS平台的供给能力仍处于紧平衡状态。剩下的事情,就是台积电按照产业实力、利润水平和市场份额分配给下游客户。因此:

CoWoS平台的封装能力决定了前沿算力的实际量产水平。

CoWoS平台的客户比例决定了算力版图的实际行业地位。

至于其他的分析,都是基于以上两点分析和结论。只要脱离了这两个论点,都是不符合行业现状的空谈和谬误,这也是我花了如此大篇幅去分析台积电CoWoS的原因,因为这就是如今全球半导体制造行业发展的主要矛盾(英伟达和台积电)的主要方面(台积电和CoWoS)。

四、从客户比例和产业实力来说:

这个地方相对就简单了,直接放上2024到2026年的主要的半导体下游客户占据的CoWoS产能的实际和预测数据:

第一大客户:英伟达

2024年占50%(17.5万片)

2025年增至63%(47.3万片)

2026年预计60%(63万片)

主要用于Blackwell(B300)和Rubin GPU。

第二大客户:博通

2024年占15%(5.25万片)

2025年13%(9.75万片)

2026年15%(15.75万片)

服务于谷歌TPU v7p 和Meta Athena ASIC。

第三大客户:AMD

2024年8%(2.8万片)

2025年8%(6万片)

2026年9.2%(9.9万片)

用于MI400X和Zen 6 Venice CPU。

其他:

亚马逊AWS(Trainium 2)、联发科(谷歌TPU v7e)等,占比12%-18%。

通过以上的CoWoS客户比例,你会明白几个产业事实:

1、英伟达的地位,持续稳固,至今无法被超越和挑战。英伟达一直占据着CoWoS平台60%的产能份额。只要这个份额不发生大的变化,英伟达就是永远的王。至于他为什么是目前永远的王,后面还会继续在第二大部分详细说。

2、博通和AMD是唯二的两个目前对英伟达行业地位构成战略挑战的叛军首领。博通的优势是ASIC+网络通讯+软件平台优势,AMD的优势是全栈的产品线优势(CPU+GUP+FPGA)。英伟达和叛军首领们如何博弈生态主导权和市场话语权,博弈的焦点在哪里,又会如何反向影响和推进芯片制造、后道封装以及设备市场,这一块也放在第二大块讲。

3、AWS、微软这样的互联网大厂和网络服务商尽管不断通过分流订单(扶持AMD、博通等),强化自研(开发自用芯片,但只能用于特定的内部场景和业务流程)等方式,力图尽量摆脱对英伟达的深度依赖,但是见效甚微。所以,对于ASIC或XPU的市场容量和替代属性过度乐观的预期,都是与目前产业实际不符的。说苛刻一点,以后A100和H100从训练退下来二线做推理,在英伟达软件生态加持下,其性能也可能是吊打其他ASIC或XPU推理性能的。

但是不论如何,通过大厂+OpenAI拉偏架叠加博通、AMD具备的特殊竞争优势,AI算力生态话语权的博弈,将在2026年步入竞争白热化的阶段,反过来,会进一步刺激巨头们对台积电最抢手的CoWoS平台的重视、投入和下注,同时推动三星、英特尔等其他二线的先进封装平台的快速发展。

以上的关于博弈和生态的事情,篇幅太大,将会集中放在第二部分去阐述和分析。

可以发现,英伟达、博通、AMD等头部厂商深度依赖CoWoS产能,推动台积电先进封装营收从2018年的15亿美元增长至2024年的超73亿美元(2024年度,台积电营收为920亿美元),2025年预计突破到110亿至120亿美元。可以想象,以后的年份,只要AI算力集群还在突飞猛进,台积电推动的后道先进封装的市场增长会远远大于前道芯片和传统封装的增速。这才是未来半导体制造业最大、最厚、最长和增速最夸张的金矿产地。所以,你看到近期爱德万、泰瑞达这么陡峭的股价走势,不要大惊小怪,因为他们占据了后道封装电测试的战略卡位,市场终究还是很聪明的。

五、第一大部分的总结

写到这个环节,楼主终于缓了一口气,这个系列的文章确实很难写,尤其是系列四,但是既然承诺过了,那就要认真写完。

整理和思考的过程是难的,总结相对就比较简单了:

🔥台积电CoWoS封装平台通过中介层实现“功能拆分+异构集成+性能集中”,成为全球半导体行业超越摩尔定律的核心技术平台。通过CoWoS,台积电构建了从晶圆制造到先进封装的垂直整合能力,占据全球高端AI芯片封装市场80%以上市场份额。剩下的是三星和英特尔,主要受限于规模化良率不足和中介层材料研发不够。比如三星的良率目前还不到70%。除GPU外,CoWoS已扩展至AI加速卡(如亚马逊Trainium系列)、网络处理器(如博通Tomahawk系列)、汽车电子、AI边缘等领域,成为高性能计算的核心封装方案。

因此,看算力生态进展和博弈,第一要务是紧盯台积电工艺进化、英伟达架构迭代和CoWoS客户比例变化,其次才是互联网大厂的小九九和博通、AMD叛军首领们的生态圈争夺进展,再次才是三星、英特尔封装进展(毛估估是落后三年)。这个世界,不缺顶尖的设计师,缺的其实是生态垄断和工匠实现。

🔥台积电现在的技术线路趋势已经加快往CoWoS-S6、CoWoS-R2、CoWoS-L2、下一代CoPoS以及更高层级和更高维度的光-电-逻辑-存储共封装集成(CoWoS+COUPE+SoIC)等多技术线路方向大踏步前进,算是一步领先,步步领先,多点开花,一骑绝尘,短期内很难以被追赶上。

不知道你们有没有看过修真小说或者佛家典籍对大小千世界观的设定,我觉得可以借用一下,台积电凭一己的连绵不断的生猛之力,硬生生把传统后道封装这个普通世界从一个“简单俗世”累积进化成了丰富多彩的“小千世界”,并快速向广袤无边、混沌模糊的“中千世界”和“大千世界”演进。简单俗世是电测试的单调和低值,而小千世界是相对复杂的电铜互联、逻辑-存储集成,到了中千世界是照进了创始之光和3D堆叠的“光-电-逻辑-存储”的立体耦合,我想象的大千世界,则是加入了量子光的混沌和无边。以上只是我突发奇思的产业幻想,大家把这一段当成小说去看更好。

🔥“前道芯片微缩已止,后道封装集成为王”的时代,正加速向我们走来,这件事已然是越来越清晰了。谁才是越过小千世界,迈入中千世界,横跨大千世界的产业主角们?才是我们需要认真深度思考的问题。

以罗博特科的ficonTEC为例吧,ficonTEC的主业是高精度微组装和光电集成测试,它多年的技术积累,正是为如今的集成封装和光电互联而生的。它目前集中力量服务的主要就是台积电的CoWoS各类平台的迭代和升级。

1、正在支撑和解决的核心流程和瓶颈问题:高精度微组装(光电子器件贴装、光纤阵列耦合)、先进封装测试(晶圆级光电测试、动态热性能测试)、工艺协同优化(键合工艺集成、亚微米级缺陷检测与修复);解决硅光集成的关键瓶颈;支撑3D堆叠的工艺革新;突破量产中的良率天花板。

2、未来技术储备:量子计算芯片封装(提供超低温环境下的纳米级对准),支持超导量子比特与控制电路的3D堆叠;车载激光雷达模块:在CoWoS衍生平台上,用于激光雷达发射/接收模块的光学相控阵集成,实现±30°视场角的高精度扫描。

3、绑定和支撑的服务方案:工程样机联合开发模式,帮助台积电提前验证未来三到五年的工艺需求。例如,双方合作开发的12轴耦合系统已完成实验室验证,可支持下一代CoWoS-X平台2.5D/3D混合堆叠的纳米级对准,为2027年量产做准备。这种深度绑定使台积电的技术迭代周期缩短,研发成本降低。还有,在CoWoS平台上,通过ficonTEC设备实现硅光芯片与电芯片的多芯片异构集成,支持CPO方案中200G/lane的高速光信号传输。

4、这样做的主要好处:

(1)、共生共荣巩固技术护城河:ficonTEC的设备,帮助台积电在CoWoS领域建立工艺-设备-材料闭环,例如其独家的硅光耦合视觉专利覆盖全球87%的相关专利和技术,形成事实上的壁垒。这种合作模式使台积电在CPO等前沿领域领先竞争对手,确保其在英伟达、博通等大客户中的共封装光学产品的不可替代性。

(2)、设备模块化帮助CoWoS提升产能弹性:通过部署ficonTEC的模块化设备架构,可以帮助台积电快速切换CoWoS不同平台的生产,产线切换时间缩短。

(3)、构建捆绑式的产业生态壁垒:通过CoWoS+COUPE+SoIC技术捆绑,核心客户(如英伟达、博通等)使用台积电和ficonTEC的一体化设备,形成 “先进制程+先进封装+光电互联”的三位一体生态。这种模式不仅锁定客户资源,还通过设备数据反馈持续优化工艺参数,提升整套设备能力,形成极其有利于ficonTEC后续持续竞争优势的数据-工艺-设备的正向循环和生态壁垒。

这里说一个题外话,CPO本质上指的就是共封装光学,最早是英特尔开始搞的,但是从当前量产上狭义的理解,就是台积电分别跟英伟达和博通分别推进的交换机等新产品,国内真正参与到这个供应链的企业很少,有少部分的光学器材厂(天孚之类),但是从封装技术工艺和平台深度参与来说,目前大陆只有罗博特科一家企业。所以,你要分清楚CPO、硅光集成和光模块的区别,至于市场所认定的奇奇怪怪的CPO概念,你就当个笑话看就可以。包括以后要搞得广义的CPO,也就是黄仁勋所说的要花二十年完成的硅光子技术,它的主要工作预计都会在台积电CoWoS这个封装平台上不断试验、验证、集成、导入和完成并推向经济化的量产,光通讯和光电集成,将是下一个封装的中千世界形成的关键元素之一,罗博特科的ficonTEC有幸能够成为台积电背后的强力辅助,并将持续享受这种暴力美学般的成长性。再远一点,量子耦合的大千世界,也会有它!

所以,不论是先进后道封装的快速进化,还是算力生态竞争的日趋白热,这一切对谁最有利?当然是能够深度嵌入台积电CoWoS平台的技术迭代和量产流程,不仅能够不断解决当前工艺瓶颈,更能够为未来三到五年的持续技术突破提供强力支撑,实现在特定领域的战略卡位和角色上的不可或缺的公司。

更重要的是,连台积电和英伟达都能支撑好,服务好,绑定好,那么三星、英特尔还有其他的芯片FAB厂和争一杯羹的封测厂、器件厂呢?这是一个不论整体竞争格局如何演化,都稳坐钓鱼台,稳稳占据产业强劲增量风口和稳赚不赔的黄金确定性。投资,最稀缺的,最难锚定的,就是战略和方向上的确定性。天下投资,唯厚重的确定性不可破。

所以,如果你投资罗博特科这种的战略稀缺企业,你的投资信念,就是来源于确定性这三个字,剩下的,是要忍受分歧,经历波动,耐心等待最大的果实成熟。

以上,供大家参考,再次且屡次说明,由于作者是一个新手,能力有限,大家把系列一到系列三都当成一个查找初级资料的小白文档去看。本系列文章(从系列一到系列四)也都只是作者通过网络资料和自身分析观点所做的整合,不提供任何投资建议!投资需谨慎!切记,切记!

为方便大家回溯,以前系列的目录如下:

罗博特科研究系列一:ficonTEC的业务组织模式:披着设备商外衣的轻资产软件系统集成商

🔥这一篇,亮出了作者第一个与市场共识完全不同的鲜明观点:ficonTEC不是重资产设备商,而是轻资产集成商。

罗博特科系列二:ficonTEC“光魔法”技术的应用范围和拓展空间—从全球半导体的封测瓶颈突破,走向泛高端制造场景的“光”赋能

🔥这一篇,亮出了作者第二个鲜明的观点:ficonTEC的产业实质和基础不是光模块或CPO,而是以全球泛半导体制造产业为基石的高端制造瓶颈场景的“光”赋能。

罗博特科系列三:“欧洲原创高端技术+中国高效工程复制”,ficonTEC的目标市场是全球泛半导体产业链

🔥系列三只说一件事,那就是通过欧洲原创高端技术+中国工程复制能力的化学反应,我认为ficonTEC的终极目标,是以前沿技术研发为发展动力,以工艺知识数据库为核心资产,以半导体巨头合作为拓展模式,成为全球泛半导体测试和制造领域的光巨头。

罗博特科系列四-1:芯片制程摩尔时代成长起来的前道工序设备王者美国科磊(KLA)

🔥作者讲述了成立于1976年硅谷的美国科磊公司,是如何全程见证并深度参与了半导体在摩尔定律推动下,单芯片微缩制程持续优化和能效持续提升的辉煌历史,这是芯片设备商深度绑定芯片巨头摩尔定律演进、精准解决半导体制造痛点,并伴随全球芯片升级和产业扩张而发展壮大的经典案例。

罗博特科系列四-2:摩尔时代步入黄昏,后摩尔时代高性能算力制造与AI工厂集群能力提升路在何方?

🔥为什么是美国科磊成为了那个时代的芯片测试设备商王者,不是爱德万,也不是泰瑞达?这个问题的背后,其实隐藏着一个至理名言,那就是:要去鱼多的地方捕鱼。投资逻辑是这样,产业逻辑更是这样。后摩尔时代,AI算力工厂集成时代,AGI强人工智能发展时代,半导体产业的“关中”还是芯片微缩制程吗?如果不是,那又该轮到什么环节了?谁又会成为后摩尔新时代的设备之王和新科磊?作者在这篇里详细分析了这个问题。