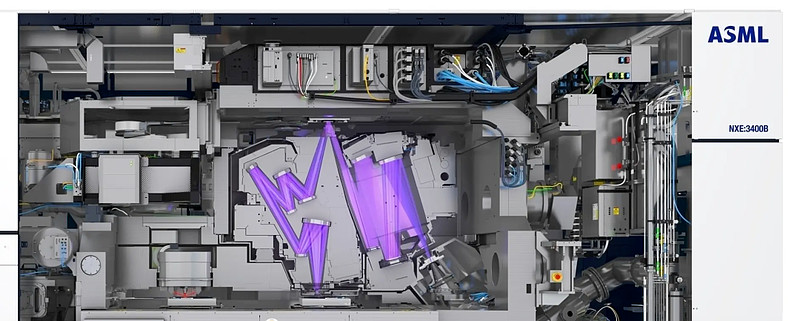

ASML发布1000W EUV光刻机——我在2025年初提出EUV光源技术设想,竟然被ASML工程师做成了现实

——我在2025年初提出EUV光源技术设想,竟然被ASML工程师做成了现实。

好久没讨论光刻机。

最近ASML发布EUV进展,光源功率由600W提升至1000W,产能可由每小时220片提升至330片。

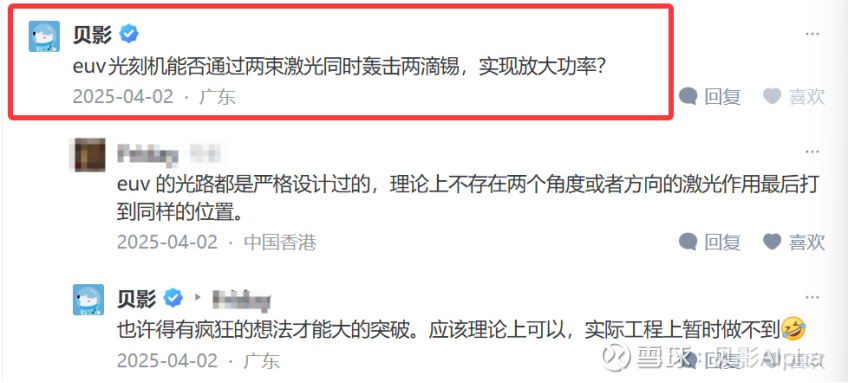

看到这则报道,不是惊讶功率有多高,而是惊喜发现:我在2025年4月2日在知乎某光刻机贴下,提出“双脉冲轰击双锡滴”提高功率的想法,被ASML工程师实现了。

正文:

光刻机的“暴力美学”:从1000W光源到英伟达的“大芯片”之谜

在芯片制造的微观世界里,有一场关于“光”的战争。为什么ASML要拼命把灯泡换成1000W?为什么台积电守着“旧机器”不放?让我们拨开迷雾。

一、为什么“灯泡”更亮,芯片就能多造50%?

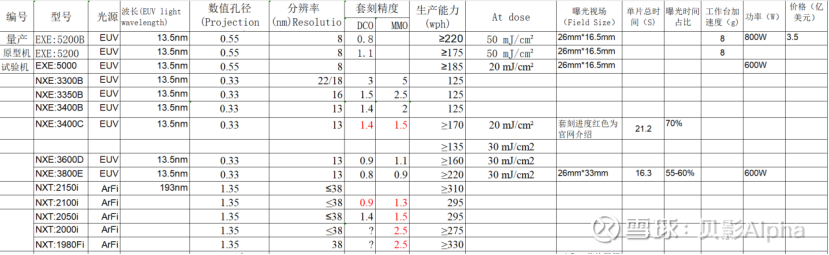

先参考一则光刻机参数表:

1.晶圆吞吐量,是指每小时光刻机处理晶圆片数量,单位用wph(waferperhour)

首先,我们要理解光刻机的产能(wph),其实就是一个简单的数学公式:

单台光刻机处理一片晶圆的总时间主要由两部分组成:

T=T1+T2

T1(间接时间):包括装载/卸载晶圆、对准(Alignment)、量测、以及工作台(Stage)在不同曝光点之间移动的机械时间。俗话说就是,像换底片、对焦、把镜头挪到下一个坑位。这靠的是磁悬浮工件台的“凌波微步”。

T2(曝光时间):光束真正打在晶圆上的时间。

2.痛点——EUV光子是“穷光蛋”

EUV(极紫外光)非常娇贵,经过十几面反射镜的“层层剥扣”,到达晶圆时能量只剩不到2%。

如果光源只有600W,光刻胶就像在阴天晒衣服,半天干不了(T2时间太长)。

3.逻辑——大力出奇迹

当光源功率从600W轰到1000W,单位时间内砸向晶圆的光子变多了。

(1)效果:曝光时间(T2)按比例缩短。

(2)结果:就像从手电筒换成了探射灯,“快门”一闪即过,每小时产出的晶圆(wph)直接飙升50%!

二、视场“缩水”之谜:High-NA的进击与尴尬

光刻机不仅在比功率,还在比“眼睛”——也就是NA(数值孔径)。

1.视野缩减:放大倍率的代价

标准版(0.33NA):视野是大开大合的26mm*33mm。

尊享版(0.55NAHigh-NA):视野缩水成了26mm*16.5mm。

形象解释一下。以前刷一次墙能刷2米高,现在为了刷得更精细(分辨率更高),刷子短了一半。结果就是:同样的墙,你要多刷一倍的次数。这就是为什么High-NA机器如果不加功率,产能反而会掉下来的原因。

2.光刻胶的“重口味”

High-NA机器(如EXE:5200B)配套的是金属氧化物光刻胶(MOR)。

30mJ vs 50mJ:以前的胶30焦耳就“饱”了,现在的金属胶要50焦耳才起反应。

为什么这么费劲?因为光子分布是随机的(散粒噪声)。光子打得越多,图案边缘就越整齐(低LER),就像用更细的针扎出的纹身,边缘才不会发虚。

三、揭秘:为什么台积电坚守“旧爱”,不急着上High-NA?

1.“大披萨”放不下“小烤箱”

0.33NA(旧款):曝光视场上限是858mm^2(实际可用约815mm^2)。

0.55NA(新款):视场上限直接腰斩到413mm^2。

关键点来了:英伟达最顶级的算力芯片(如GB300的单Die),面积恰好就在814mm^2左右,紧贴着旧款机器的极限!

2.台积电的“小算盘”

如果台积电现在全面换装High-NA,英伟达的大芯片就会因为“烤箱太小”而被切成两半。

解决方案:必须用复杂的“缝合技术(Stitching)”,把两个半场拼在一起。这不仅成本高,良率还会掉到坑里。

现状:台积电用0.33NA的老机器,配合“多重曝光”,既能保住英伟达的大芯片面积,成本还更低。

结论:那些早早冲进High-NA的厂家(比如英特尔),虽然在1.8nm工艺上抢了先,但在生产“算力巨兽”大芯片时,反而面临无机可用的尴尬。

$台积电(TSM)$ $阿斯麦(ASML)$ $福晶科技(SZ002222)$