200G/Lane时代,NPO优于CPO

本文将深入剖析NPO(近封装光学)以及CPO(共封装光学) 这两种核心方案,从功耗、延时、成本、SerDes插损、生产制造良率、网络可靠性等多个维度进行系统对比。

一、 技术原理与核心差异

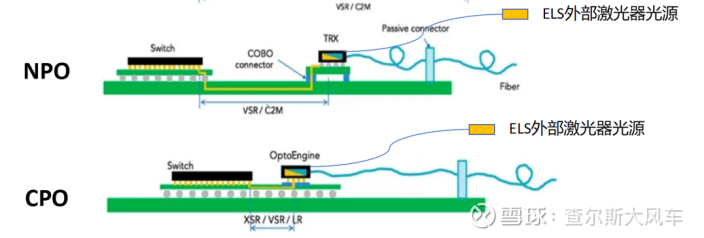

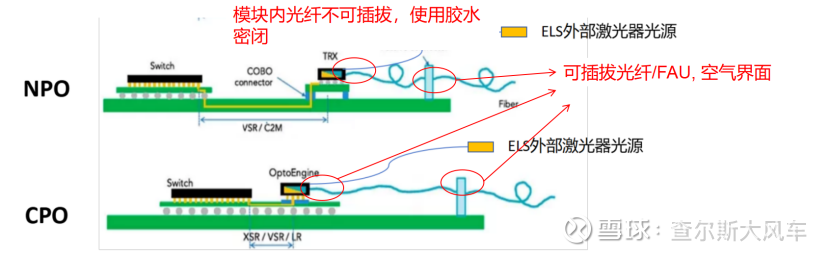

一张图表示一下2个方案的区别

这2个方案,都有一个明显的特征,就是支持无oDSP,发送侧Serdes 直驱Driver,TIA/LNA 之后,直接连接Serdes,完全使用Serdes里面的oDSP来校传统通道上的插损、噪声。

各个方案的主要区别是:

NPO方案:

交换芯片 -> 芯片封装基板 -> 基板走线 -> BGA 球 连接PCB -> PCB 走线 -> 连接器-> 光模块板上PCB走线 -> 光电芯片BGA -> 光电芯片基板 -> 光电芯片

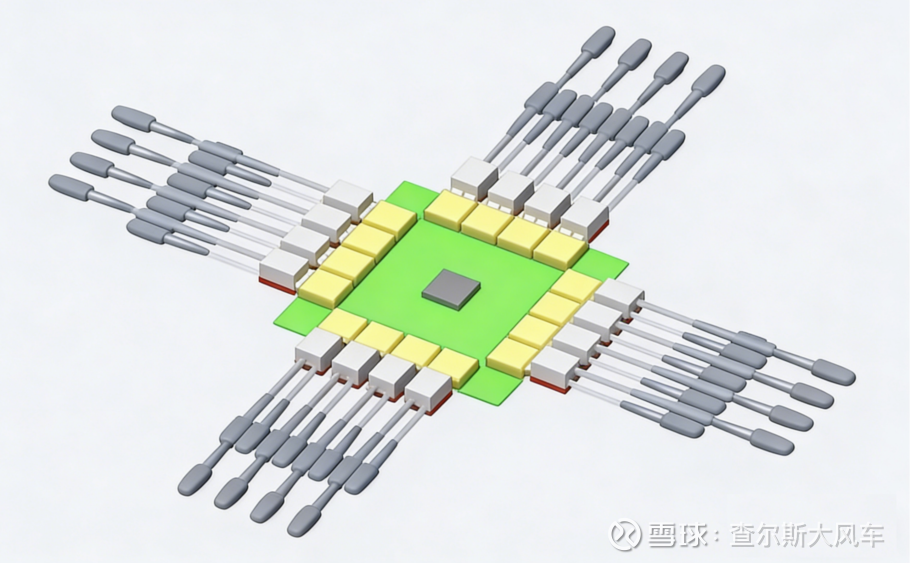

CPO方案:

交换芯片 -> 芯片封装基板 -> 基板走线 -> 光电芯片基板 -> 光电芯片

二、 多维度性能对比

性能:

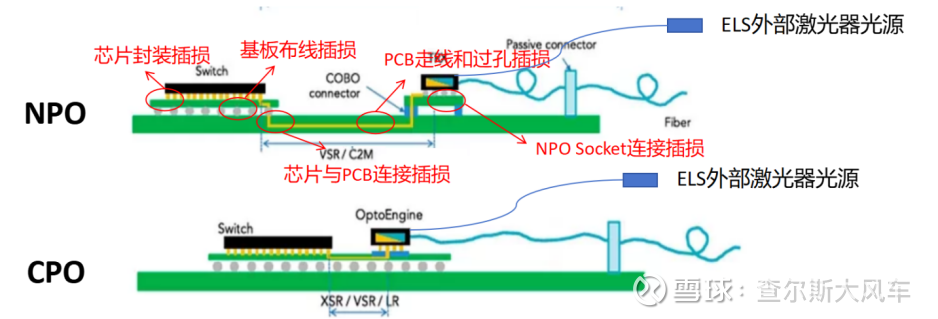

各个部分的插损介绍:

1. 芯片封装插损

芯片Die到基板的金线连接插损,一般~1dB

2. 基板布线插损

基板走线到芯片底部Bump的插损,平均走线2cm,考虑CPC封装和CPO封装平均走线4cm;

3. 芯片基板与PCB的连接插损

4. PCB走线与过孔插损

(1) NPO考虑走线距离10cm,使用M9 PCB

可以计算得到各个方案的Serdes 走线插损:

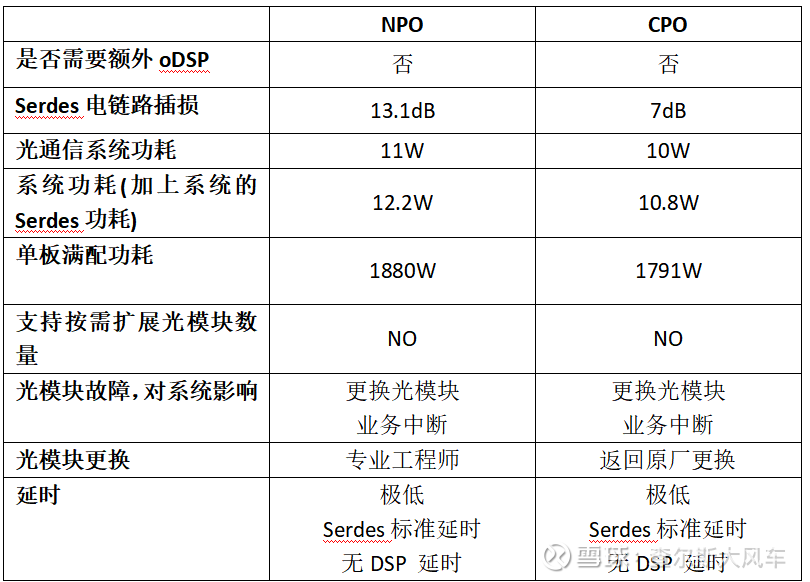

上图可以看到CPO插损最7dB,NPO插损13.1dB。 这两个插损差别不大,只需要Serdes的规格升一级,从XSR 升级VSR 即可,每条serde 的功耗增加50mw。

224G SerDes 规格与插损覆盖对比表

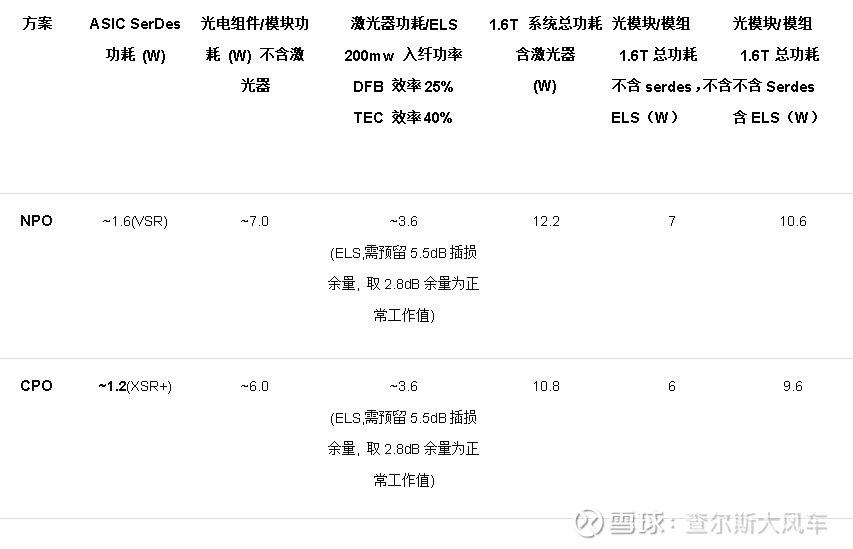

可以得到,NPO和CPO方案的功耗对比如下:

整体结论是1.6T系统上,NPO功耗比CPO多1.4W, 整个单板满配下,多89.6W, 这个对于整个单板2000W左右的功耗来说,差别不大。

到这里来说CPO相对于NPO来说,功耗和性能上略有优势,其他方面二者基本持平。东山精密的LPO 模块甚至比表中的11W功耗还要低,可以到9W左右;

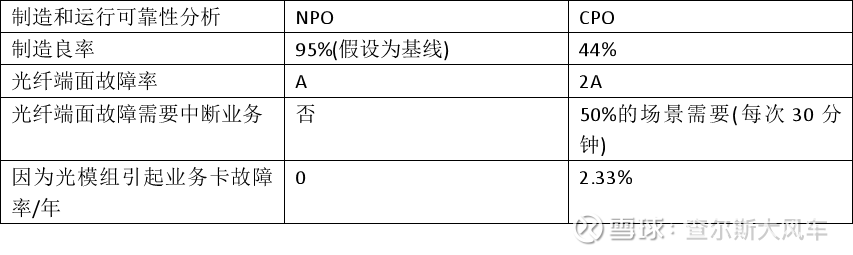

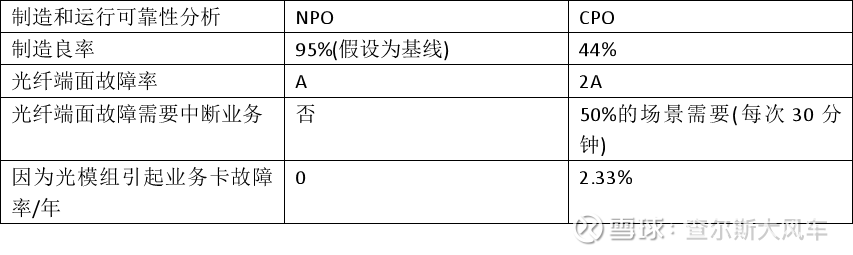

二、制造良率和运行可靠新对比

1. 制造良率:

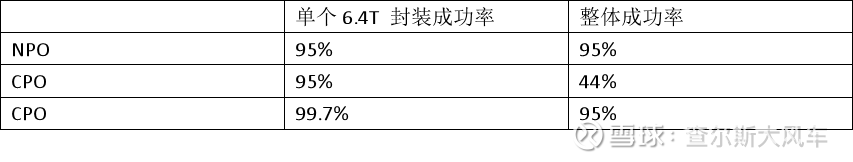

对于NPO来说,每一个NPO模块比如6.4T (32x200G)模块,中际旭创和新易盛在OFC 2026上都发布了6.4T 的NPO模块。假设工艺成熟后,每个NPO模组封装的良率是95%;然后整体的良率也就是95%, 因为这个NPO模块是单个的封装的;

而对于CPO 来说,512条Serdes的交换芯片,有16个6.4T 模块,只要有一个生产时坏了,整体就坏了。 假设单个6.4T 模块CPO光模组封装的成功率是95%;那么这个芯片+光的成功率只有44%;因为他需要这个16个全部不坏,才能保证整体是成功的。

看到如果要达到NPO 相同的95% 的封装成功率,单个6.4T的封装成功率,要高达99.7%,相当于不良率从5%, 需要降低到0.3%, 降低了15倍以上,这个需要付出巨大的工程研发成本、时间周期、高精度的仪器仪表的成本,这也是制约CPO 商业的卡脖子点之一。

2、网络运行的可靠性:

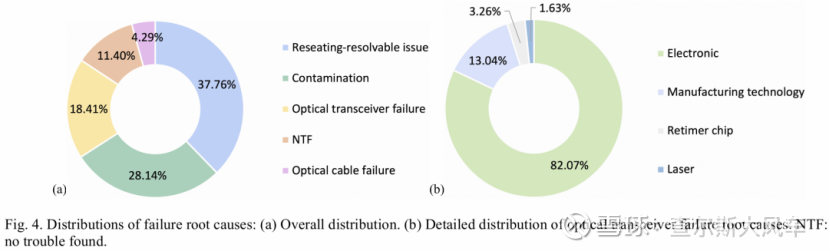

阿里在OFC 2026里面发表了一篇论文:Field Operation Data Analysis of Optical Interconnects in AI Computing Networks;里面介绍了,400G DR4光模块的总体故障率是0.21%@2年,DR4 平均每年可以近似为故障率0.1%;

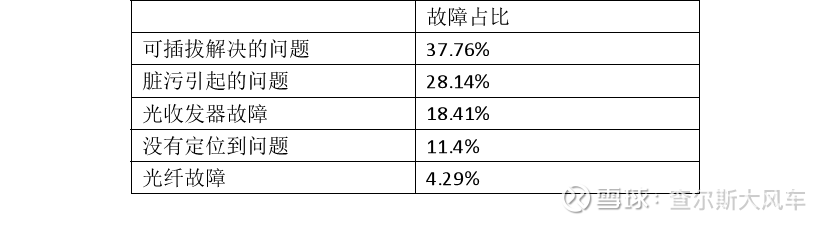

2.1 光纤端面脏污问题

可以看到需要插拔或者因为端面脏污等引起的问题占到故障率整体的84.31%。

因为CPO的空气光纤端面数目比NPO多一倍:(CPO 必须要做FAU 可插拔,它不可能带着尾纤上SMT 焊接机 )

所以CPO 有卡插拔FAU和面板MPO 两个空气光纤端面,由于水汽和灰尘的进入,将导致光纤的故障。 而NPO 只有面板MPO 一个光端空气端面,所以, CPO的光纤端面故障率预计比NPO多一倍;对于CPO 来说,如果光纤端面故障发生在FAU 出,将需要断电,拔除单板清洁;至少中断30分钟;

2.2 收发器故障问题:

收发器故障占到整体故障率的18.41%, 也就是说相当于DR4每年的故障率是:0.01841%。 而一个512条Serdes的交换芯片,它相当于128个DR4。 这个128个DR4 每年全部不故障的概率是:97.67%;也就是故障的概率是:2.33%。 对于一个万卡的算力中心来说,几乎每天都会有算力卡故障,每次故障带来30分钟的业务中断,这将大幅降低AI GPU集群的可靠性、可服务性。

总结:

NPO 大幅领先CPO,:

1. 从功耗、性能上来说200G/Lane 时代NPO 和CPO 相近;

功耗:NPO 1880W vs CPO 1791W, 相差90W, 小于5%;

性能:NPO 13.1dB 插损 vs CPO 7dDB 插损, 分别使用VSR 和XSR serdes都可以解决,都是低功耗的Serdes。 无需额外的DSP;

2. 但从制造成本、AI 算力网络系统的可靠性来说,NPO 远远优于CPO;